CPU缓存和TLB都是微处理器中使用的硬件, 但是有什么区别, 特别是当有人说TLB也是一种缓存时?

首先是第一件事。CPU缓存是一种快速存储器, 用于提高从主存储器(RAM)到CPU寄存器的信息获取延迟。因此, CPU缓存位于主内存和CPU之间。并且此缓存临时存储信息, 以便对相同信息的下一次访问更快。用于存储可执行指令的CPU缓存, 称为指令缓存(I-Cache)。用于存储数据的CPU缓存, 称为数据缓存(D-Cache)。因此, I-Cache和D-Cache分别加快了指令和数据的获取时间。现代处理器同时包含I-Cache和D-Cache。为了完整起见, 让我们也讨论D缓存层次结构。 D-Cache通常按层次结构进行组织, 即1级数据高速缓存, 2级数据高速缓存等。应注意, 与L2 D-Cache相比, L1 D-Cache更快/更小/更昂贵。但是”CPU缓存‘是为了加快从主内存到CPU的指令/数据获取时间。

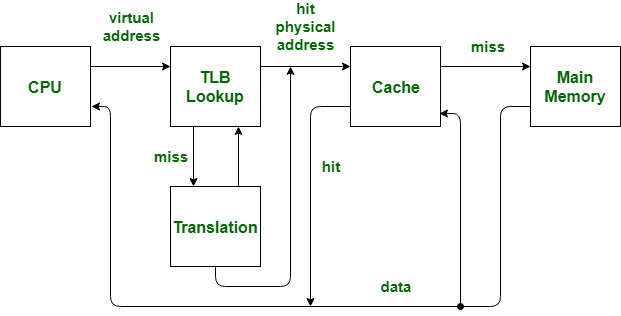

翻译后备缓冲区(即TLB)仅当处理器使用虚拟内存时才需要。简而言之, TLB通过将页表存储在更快的内存中来加快虚拟地址到物理地址的转换。实际上, TLB也位于CPU和主内存之间。准确地说, 当虚拟地址需要转换为物理地址时, MMU使用TLB。通过将虚拟物理地址的这种映射保留在快速存储器中, 可以改善对页表的访问。应该注意的是, 页表(其本身存储在RAM中)会跟踪虚拟页在物理内存中的存储位置。从这个意义上讲, TLB也可以被视为页表的缓存。

但操作范围为TLB和CPU缓存e是不同的。 TLB的目的是”加速虚拟内存的地址转换”, 这样就不必为每个地址都访问页表。 CPU高速缓存旨在”加快主存储器的访问延迟”, 从而使CPU不会总是访问RAM。 TLB操作在MMU进行地址转换时发生, 而CPU缓存操作在CPU进行内存访问时发生。实际上, 任何现代处理器都可以部署所有I-Cache, L1和L2 D-Cache和TLB。

如果你觉得以上有用, 请做点赞/分享。另外, 请留下你的评论以进一步澄清或获取信息。我们很乐意帮助和学习?

srcmini

srcmini

评论前必须登录!

注册